真值表推算门电路逻辑与化简

前言

这是我大学还是一名籍籍无名的做题家时记下的笔记,主要是为了做题,但其实还是有实际意义的,从实际需要写出真值表,从真值表推算门电路逻辑,然后选取合适的电路设计。

有点感慨,当初的文字略显青涩还啰嗦,如今除了不是做题家还是和那时一样。

推门电路核心四步

- 列真值表,筛选出输出Y=1的所有行(输出为0的行不用管,简化工作量);

- 每一行的变量组合,写成一个“最小项”(与项,比如A=0、B=1,就是A’B);

- 所有最小项用“或”(+)连接,得到原始的与-或标准式;

- 化简(用套路、极简公式、卡诺图)。

肉眼化简套路

约定:A' = A非(取反),· = 逻辑与(可省略,比如AB就是A·B),+ = 逻辑或

- 互补抵消

A + A' = 1(一正一反或运算,直接等于1,比如A+A’BC = 1·BC = BC)A·A' = 0(一正一反相乘,直接等于0,比如A·A’B = 0·B = 0)

- 重复项删除

A + A = A(不管写多少次,只留1个)A·A = A(同理,重复的与项只留1个)

- 短项吸收长项

A + AB = A(只要有单独的A,带A的长项全删,比如A + ABC + ABD = A)A + A'B = A + B(留正项,去掉反项,比如A + A’BC = A + BC)

- 成对消去相反变量

AB + AB' = A(B和B’相反,直接消去,只剩相同的A)A'B + AB = B(同理,A和A’相反,消去后只剩B)

- 交叉冗余项删除

AB + A'C + BC = AB + A'C(BC是冗余项,直接删,再比如AB + A’C + ABC = AB + A’C)

对于第五点,交叉冗余项,其中含义是有两项中有一个输入符号相同,相性想法,另外两个符号不同,而交叉冗余项就是取了那俩不同符号的项目,直接与上那个相同符号的1就行,,解释一下:

上面的符号,A是两项都有且相性相反的,BC是不同符号组合的项,那么直接与上A组合的1 -> BC(A+A') = ABC + A'BC,其中A+A'就是1,然后短项吃掉长项,就得到结果了。

公式

| 公式 | 备注 |

|---|---|

| A + 1 = 1;A + 0 = A | 或运算:遇1则1,遇0不变 |

| A·0 = 0;A·1 = A | 与运算:遇0则0,遇1不变 |

| A + A’ = 1;A·A’ = 0 | 互补律,最常用,一眼识别 |

| A + B = B + A;AB = BA | 交换律,顺序随便换,不影响结果 |

| A(B + C) = AB + AC | 分配律,拆开括号用,化简常用 |

| A + AB = A | 短项吸长项,记“短吃长” |

| A + A’B = A + B | 留正去反,记“删反项,留正项” |

| (A+B)’ = A’B’;(AB)’ = A’+B’ | 德摩根定律,取反用,记“或变与、与变或,全取反” |

卡诺图化简

核心逻辑

把真值表的最小项(Y=1的项)填入方格,相邻的方格(只变1个变量)可以合并,消去变化的变量,最终得到最简与或式。

关键规则

- 方格排列:变量按“格雷码”排列(00→01→11→10),保证相邻格子只变1个变量;

- 圈格子规则:只能圈2、4、8个格子(2的n次方),圈越大越好,重叠圈没关系;

- 写表达式:每个圈里,不变的变量保留(全1留原变量,全0留反变量),变化的变量消去。

卡诺图例子

例一:2变量卡诺图(Y=AB + AB’)

变量:A、B(2变量,卡诺图2×2方格)

真值表(只列Y=1的行):

A B Y 最小项 1 0 1 AB’ 1 1 1 AB 画卡诺图(行=A,列=B,格雷码排列):

A\B 0(B’) 1(B) 0(A’) 0 0 1(A) 1 1 圈格子:把两个1圈起来(2个格子,符合规则)

化简:圈里A全是1(不变),B有0有1(变化,消去),所以Y=A(和套路4结果一致)

例二:3变量卡诺图(Y=A’BC + ABC + AB’C + A’B’C)

变量:A、B、C(3变量,卡诺图2×4方格)

真值表(Y=1的行):

A B C Y 最小项 0 0 1 1 A’B’C 0 1 1 1 A’BC 1 0 1 1 AB’C 1 1 1 1 ABC 画卡诺图(行=A,列=BC,列按00→01→11→10排列):

A\BC 00 01 11 10 0(A’) 0 0 1 0 1(A) 0 0 1 0 (补充:3变量卡诺图行是A(0、1),列是BC(00、01、11、10),上面4个格子对应A=0,下面4个对应A=1;Y=1的格子是(A’,BC=11)、(A,BC=11)、(A’,BC=01)、(A,BC=10))

圈格子:把4个1圈成一个大圈(4个格子,符合规则)

化简:圈里C全是1(不变),A有0有1、B有0有1(变化,消去),所以Y=C

例三:4变量卡诺图(Y=ABCD + ABC’D + AB’CD + AB’C’D + A’BCD + A’BC’D)

变量:A、B、C、D(4变量,卡诺图4×4方格)

真值表(Y=1的行,只列最小项):ABCD、ABC’D、AB’CD、AB’C’D、A’BCD、A’BC’D

画卡诺图(行=AB,列=CD,均按格雷码00→01→11→10排列):

AB\CD 00 01 11 10 00(A’B’) 0 0 0 0 01(A’B) 0 1 1 0 11(AB) 0 1 1 0 10(AB’) 0 1 1 0 圈格子:

- 第一圈:(A’B,CD=01)、(A’B,CD=11)、(AB,CD=01)、(AB,CD=11)→ 4个格子

- 第二圈:(AB’,CD=01)、(AB’,CD=11)→ 2个格子

化简:

- 第一圈:B全是1,D全是1,A有0有1(消去),C有0有1(消去) → 表达式:BD

- 第二圈:A全是1,B全是0(B’),C有0有1(消去),D全是1→ 表达式:AB’D

- 最终最简式:Y = BD + AB’D = D(B+AB’) = AD + BD

逻辑表达式化简练习

习题一:原始式 Y = A’BC + ABC + AB’C

- 用套路化简:

- 前两项:A’BC + ABC = BC(A和A’相反,消去A)

- 剩余:BC + AB’C = C(B + AB’) = C(A + B)(用套路3:A + AB’ = A + B)

- 最简式:Y = C(A + B) = AC + BC

- 用卡诺图验证:3变量,Y=1的最小项是A’BC、ABC、AB’C,圈格子后得到同样结果。

习题二:原始式 Y = AB + A’C + BC + ABC

- 用套路化简:

- 先删冗余项:AB + A’C + BC(ABC被AB吸收,删去)

- 再删冗余项:AB + A’C(BC是冗余项,删去)

- 最简式:Y = AB + A’C

- 用卡诺图验证:3变量,圈格子后,AB和A’C两个圈,无冗余,结果一致。

SR锁存器逻辑式推算

像加法器、逻辑译码等电路,都属于组合逻辑电路:输出结果仅由当前时刻的输入唯一决定,电路无记忆能力。但除此之外,数字电路还有另一大类:时序逻辑电路,又分为同步时序与异步时序。

时序逻辑和组合逻辑最核心的区别是:具备状态记忆功能,输出不仅取决于当前输入,还依赖电路上一时刻的历史状态。而实现记忆的关键,就是引入反馈环路,将电路的输出反向接入自身输入端,以此锁住、保存数据状态,这也是锁存器这类电路能够存储 1 位数据的根本原理。

无论是哪种逻辑电路,推算逻辑表达式都万变不离其宗,下面推算一个SR锁存器的逻辑表达式。

首先明确SR锁存器的核心变量,它作为异步时序逻辑电路,推算时必须引入旧状态Qₙ(上一时刻的输出,体现记忆功能),输入为置1端S、置0端R,输出为新状态Qₙ₊₁(下一时刻的输出),同时排除S=1、R=1的非法状态(禁止使用,不参与表达式推导)。其完整特性表如下(仅保留有效状态):

异步时序靠自身线路反馈自行锁住状态、随时变化;同步时序必须等外部时钟CLK信号触发,才会统一更新状态。

| S | R | 旧状态Qₙ | 新状态Qₙ₊₁ | 功能 |

|---|---|---|---|---|

| 0 | 0 | 0 | × 非法禁用 | 禁止 |

| 0 | 0 | 1 | × 非法禁用 | 禁止 |

| 0 | 1 | 0 | 0 | 复位清0 |

| 0 | 1 | 1 | 0 | 复位清0 |

| 1 | 0 | 0 | 1 | 置位写1 |

| 1 | 0 | 1 | 1 | 置位写1 |

| 1 | 1 | 0 | 0 | 保持 |

| 1 | 1 | 1 | 1 | 保持 |

首先,去除禁止行,不参与推算。

然后沿用组合逻辑的推算思路,只筛选出 新状态 的行,写出对应的最小项(输入变量为 ,三者均为1时构成最小项):

接下来进行化简,得:

用德摩根定律可以得到这样的式子:

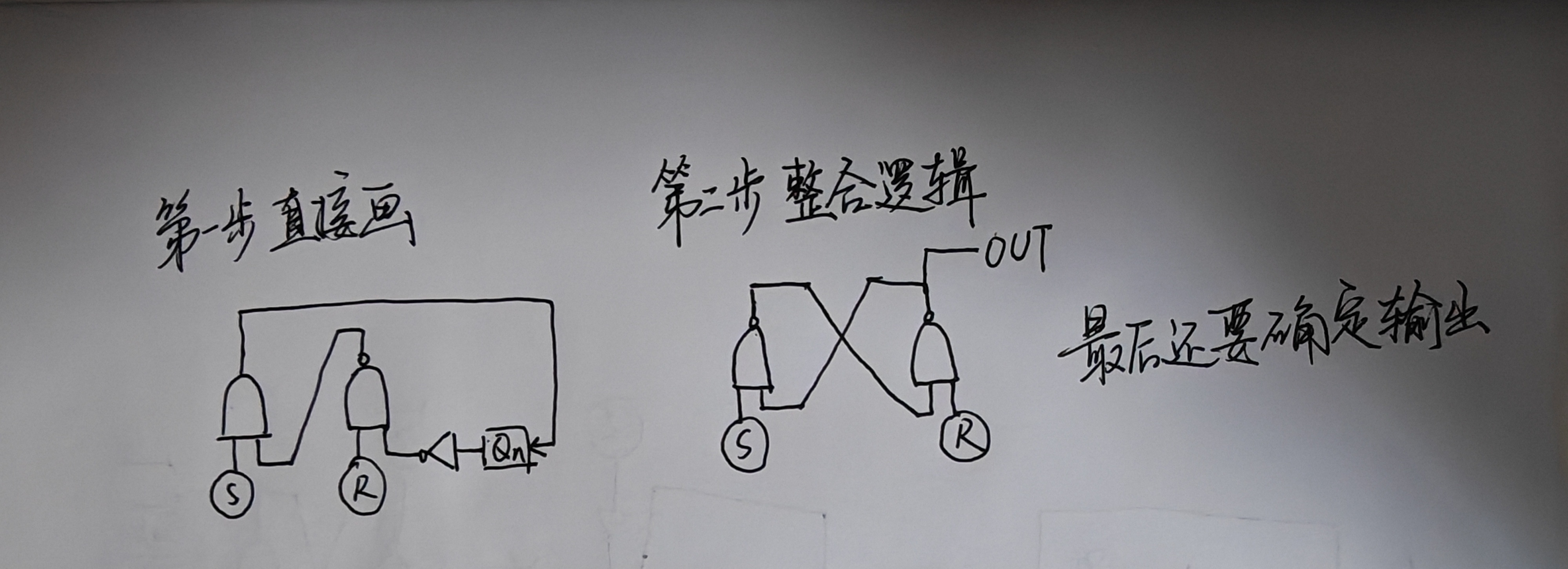

这样就只剩下与门和非门了,然后我们就能得到他的电路(先把Qn当做一个电路黑盒画出来,后面直接把式子输出替代Qn即可)

注意,这只是一种SR锁存器,还有别的类型;这里的SR锁存器是低有效的,即0触发动作,因为真值表是s和r都为1时保持数据,当他们变到0时才会触发置位或复位动作。

这里的输出是这样确定的,把两个与非门输出定义为G1(左),G2(右);然后就能得到:

然后把S=1,R=0,输出为1的置位功能参数代入,就得到了G2输出一定为1,由此判定G2为输出Q,G1为输出Q’。

需要使用SR锁存器的话,只要推断S(置位)的表达式,R(复位)的表达式接入上面的结构即可(这句话实际是错误的,因为还要考虑如何不可达非定义状态,即S和R不能同时为0)。

实际电路设计

实际的电路设计比纸上谈兵的结果要复杂,毕竟书面上是理论上如何如何,实际电路是需要考虑物理特性的。

可以看看下面的视频讲解,讲到了双稳态电路,还有非定义状态(实际电路设计极力避免的情况,需要做到不定状态电路逻辑不可达,一般都是加个双稳态结构)和不定态(从非定义态转换到保持态,由于门电路延迟问题,总会有一个先变,一个后变,而且不固定,导致保持的数据不能确定),这在电路设计中都很重要,算是理解时序电路的起点吧:

【数字电子技术基础】一个视频带你彻底搞懂SR锁存器不定态和非定义状态

结语

- 化简优先级:先看套路(肉眼能化简的先化简)→ 再用公式 → 复杂的(3变量及以上)直接画卡诺图;

- 卡诺图关键:相邻格子必须只变1个变量,圈越大越简单,不用怕重叠;

- 不用死背复杂公式,记住套路和卡诺图,所有化简题都能搞定;

- 实际意义:化简后的逻辑式越简单,用的门电路越少,硬件成本越低(比如按键逻辑、IO判断,都会用到)。

- 组合逻辑电路和时序电路有所不同,实际设计电路往往要考虑更多的东西,不是按照组合逻辑连接门电路就一定能实现想要的效果。