上拉电阻和下拉电阻

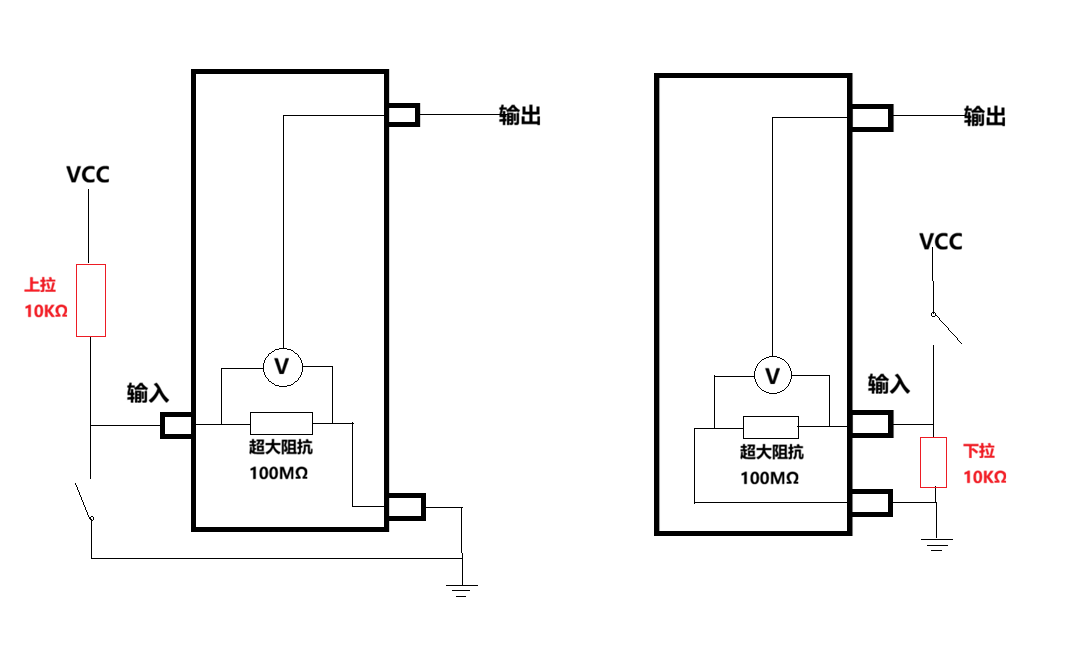

先上图,然后再了解上拉电阻和下拉电阻

上面电路图的外围电路就是我们耳熟能详的上拉电阻和下拉电阻的电路,至于内部的,当然不是我画的那样,但是是那么个意思。

输入引脚接到内部检测电压的电路,超大阻抗和那个”电压表”共同组成一个检测器,当电压表的值超过某一阈值时,向输出引脚输送电平信号1,否则输送0。

上拉电阻和下拉电阻说白了还是电阻,在了解为什么需要他们之前,我们先要了解一件事:悬空引脚电平信号不稳定。

悬空引脚意思就是没有输入引脚旁边的一堆外围电路,输入引脚不接任何线,这时候我们从输出引脚测量电平信号,往往是1010011010…这样混乱不堪的结果,并不是我们想象中的稳定输出电平信号0,至于原因,可能要了解MCU内部真正的电路结构,有MOS电路(超大阻抗就是因为接了栅极),有小电容,有施密特触发器这些东西。

(讨教了一下AI为啥悬空引脚信号不稳定)

这是因为引脚内部的MOSFET栅极像一根“天线”,会感应周围空间的电磁干扰,同时内部微小的漏电流也会让电压随机漂移,所以检测器读出的结果毫无规律。

总之人类设计的MCU,在物理世界的规则就有“悬空引脚电平信号不稳定”的问题,你说该怎么办吧。

聪明的你一定想到了:我在外围接个电源不就完事儿了。

确实,我照着做,把引脚直接接到电源正极(VCC),再把开关接在引脚和地(GND)之间。这样开关断开时,引脚一直有高电平;开关闭合时,引脚直接接地,变成低电平。

结果,我闭合开关的瞬间导线烧了…

后来有人告诉我:在电源和引脚之间串一个电阻就行了。

这个电阻在开关断开时,让引脚仍然能通过它得到高电平;在开关闭合时,它限制了从电源到地的电流,不会短路。这就是上拉电阻的由来。

上面的情景讨论,最终产物就是我们的上拉电阻电路,从最终结果上看,加上他只是为了防短路,但确实必不可少。

下拉电阻电路同理,只是开关闭合时才是高电平,断开时低电平,这更符合人类直觉,闭合开关才是开灯的那种直觉。(PS:工程中上拉更常用,很多MCU内部集成了上拉电阻)

所以,“上拉”“下拉”只是描述电路接法的专业术语——电阻接在VCC和引脚之间就叫上拉,接在GND和引脚之间就叫下拉。

说电阻“把引脚拉到高电平”,其实是省略了中间过程的结果描述。真正干活的还是电源,电阻还是用来防止烧电路。